# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCE AND RESEARCH TECHNOLOGY

## EMPIRICAL DEMONSTRATION OF NEXT GENERATION HIGH SPEED HYBRID CMOS-SET BASED CONSUMER FRIENDLY IBM MACHINE SUBSECTION

Dr. J. Gope<sup>\*</sup>, Mr. Chowdhury Tousif Ahammed and Mr. Habibur Rahman

Dept. of ECE, Camellia School of Engg. & Tech., Barasat, Kolkata, India Dept. of EE, Camellia School of Engg. & Tech., Barasat, Kolkata, India Dept. of EE, Camellia School of Engg. & Tech., Barasat, Kolkata, India

## ABSTRACT

At the very dawn of post CMOS era Single Electronics ushered new ventures in resolving power dissipation and power consumption like hindrances. Low power consuming, high speed & high integration density Single Electronics play a major role in modern nano scale electronics. It schematically focus on the movement and position of a single electron. There has been extensive research to develop specific applications of Single Electronics in Defense applications (for unmanned and remote areas), Space Technologies (such as space vehicles), medical applications (such as space-maker battery) etc. The research criteria in such applications are minimum power for maximum battery lifetime. One such revealation of implementation of Single Electronics is and the consequences are analysized to compare it with conventional technologies.

KEYWORDS: CMOS, ITRS, SET, Hybrid CMOS-SET, IBM machine subsections.

#### INTRODUCTION

The fundamental topology of device research is down scaling of device sizes. The decisive factors in down scaling are i)what would be the minimum gate length ii) What would be the minimum gate oxide thickness iii) What would be the minimum band gap etc [1-6].

Sir Gorden E. Moore, in connection to such findings stated that - the number of transistor that can be fit in single die area doubles within every 18months [7]. Such trend in device down scaling stimulated electronic industry to produce high speed low power consuming ultra dense digital circuits. But the fragility is that such down scaling is not a 'Never ending process'. The power dissipation factor proportionally increases with the down scaling of the device sizes. Thus constant device down scaling will increase temperature manifold which might be equal to the temperature of surface of Sun. Besides power dissipation is an avoidable circumstances. Other hindrances of continuous down scaling is somehow subjected to technological limitation. The same has been observed by the statement made by Gorden E. Moore in late 2003. Also International Technology for Road Map of Semiconductor (ITRS) suggested in the same fashion about the device miniaturization in 2005 [8]. Thus the concept of the 'more to Moore' technology attracted researchers worldwide in post CMOS era.

The extensive sophisticated advanced e-beam lithography technique augmented the device minimization manifold. Apparently, this brought technological sifting in effect. The new technology evoked in the context of post CMOS era are i)Carbon Nano Tube ii)Resonant Tunneling Diode iii)RFSQ iv)Quantum Electronic Device [9-12]. Quantum electronics plays an imperative role in designing next generation digital electronics. Quantum structure is excessively referred in both industry and academia owing to its unmatched credentials in device minimizing. But amid its numerous advantages over other consumer electronics, it faces major challenges like technological limitations, structure related limitation, material related limitation, process related limitation etc [13]. In such context device research coherently progressed to single electron transistor technology based on the tunnel phenomena of electrons. This phenomena is considered to be pivotal as tunneling leads to extreme manipulation of electrons in a confined region- it is attributed as the ultimate form of device research.

http://www.ijesrt.com@International Journal of Engineering Sciences & Research Technology

## ISSN: 2277-9655 (I2OR), Publication Impact Factor: 3.785 (ISRA), Impact Factor: 2.114

Thus Researchers attempted SET technology for next generation device modeling. The following section will briefly outline SET and it's methodology, some of the operational aspects of SET, few drawbacks of SET and some relevant options to resolves such drawbacks. Subsequently, the authors here propose a nano device modeling of a high valued digital logic circuit which are quite substantial and can be incorporated in IBM machines. A comparative study is also concluded at the last section of this letter to outline the modulus operandi of the stated model.

#### **SET IN BRIEF**

SET evolved as a promising elementary device that insights the charge transport phenomena. The nature of charge transport is discrete unlike other conventional devices. It comprises of two tunnel junctions that share a common electron as depicted in the fig.1 below.

The fig.1 reveals control flow of current as the SET is brought into active region. The Coulomb energy plays an impetus role ensuring proper control flow from source to drain. The tunnel junction is a composite structure of two pieces of metal, amid which a thin layer of insulator is sandwiched having thickness of 1 nm [14-17].

Electrons can granule from one side of the electrodes to the other side if and only if the coulomb energy is greater than the static energy given by  $E_c = \frac{e^2}{2c} > KT$  (1)

Where K=Boltzmann constant= $1.38 \times 10^{-34}$ J/K, T= absolute temperature. Thus, tunneling is discrete process ;the flow of electrons increases manifold (multiple of 'e's) through the tunnel junction. Here the bias voltage is less than coulomb gap voltage and if the gate voltage enhances in such situation, the energy of the initial system proportionately increases. Thereby, the energy of the system on the island gradually will diminish. One can determine the coulomb energy as the prerequisite charge of an island with electrons. The tunnel junctions are channeled to mobilize the electron independently from island to island. One interesting criteria is that the electron are strictly localized on the island and tunnel resistance is sufficiently large enough over the fundamental resistance i. e.

$$R > R_q = h/e^2 \tag{2}$$

It was empirically demonstrated by Likharev [18] that the gate voltage is critical to the corresponding slope on coulomb staircase. The quantum dots interface with the source and drain of SET electrons. The potential drop in the dot is manipulated by the gate electrons which is eventually coupled to the quantum dot  $(Q_d)$ . It ensures that when current is zero, the number of electron becomes fixed. Thereby the essential operation of SET device ensures that the tunnel junction resistance has to be greater than the quantum resistance and the charging energy i.e., quantum dot capacitance has to be larger than avoidable formal energy. It is given by

$$\mathbf{C}_{\mathbf{T}} = \mathbf{C}_{\mathbf{G}} + \mathbf{C}_{\mathbf{D}} + \mathbf{C}_{\mathbf{S}} \tag{3}$$

Where  $C_G$ =Gate capacitance,  $C_D$ =Drain capacitance,  $C_S$ =Source capacitance,  $C_T$ =Total capacitance. To simulate the tunneling phenomena one has to determine the rate of all possible tunneling events. Once tunneling occurs the circuit is free from energy changes. The co-relation between free energy 'F', electrostatic energy 'U', work done 'W ' is given by F = U - W (4)

### IF SET IS THE ALTERNATIVE THEN WHAT RESTRICT ITS INCORPORATION

The Researchers intend to scale down the computer chip rapidly, thus the idea of incorporating SETs has increased manifold. Like several other electronics devices SET insights the potential to reach the molecular scale and would confine it-self in far less space as compared to the conventional counterpart. The small size, fast inaction and low power dissipation of SET circuits make them potentially useful and best compliment for next generation IC design.

But amid all the intrinsic limitations are deliberately restricting its maximal employment in digital electronics. Researchers in their proposed study revealed few of them. Among other disadvantages, low gain, random background charge and room temperature operation stands to be extremely catastrophic. Thus an alternative was intended.

Hybrid CMOS-SET ushered new horizons in replacing CMOS. Besides it is a bridging element between CMOS and SET. Thus Researchers tend towards this promising alternative. Hybrid CMOS-SET circuits have been reported in many journals [19-21]. The authors have corroborated the same for next zen device design. Few Hybrid CMOS-SET based logic realizations have been enumerated here for perusal.

## **REVIEW OF IBM MACHINES**

The IBM machines popularized as a composite structure of several combinational logic circuits. With the incorporation of excellent logical mechanism IBM distinguished themselves as the pioneer of electronics industry since long. Here the authors considered a simple logic circuit; the same is often used in IBM machines. Interestingly, the verification combination for checking two Boolean networks consecutively is represented using functional equivalence circuits. Topologically their performance amends due to technological development of optimization, although it has to reflect the same behavior as in before. Many published articles do resemble many methods that has been proposed efficiently and satisfactorily. Here the authors propose a novel architecture used by IBM machines, the same CMOS based circuit has been realized magnificently as a serial adder in many of their application.

### **PROPOSED MODEL**

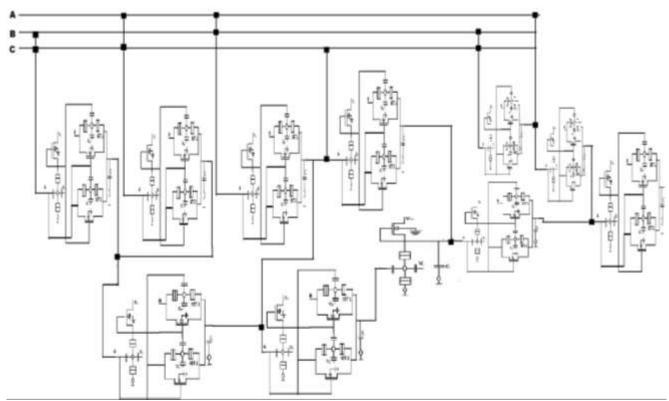

The circuit realized in Fig4 is capable to perform arithmetic and logic operations and the same can be integrated into a nano scaled IC which can be fitted to any present day available real time systems. When digital signals are transmitted from one point to another a noise impulse is created and that changes the logic level of the data bit.

The circuit comprises of 5 hybrid CMOS-SET based AND gates 3 hybrid CMOS-SET based OR gates and one hybrid CMOS-SET Inverter. The AND gates A1,A2,A3,A4 along with the OR gates O1,O2,O3 gives and output that equals to

C out =A.B+B.Ci+A.Ci

This output is driven to OR gates O2 through a hybrid CMOS-SET Inverter circuit. Thus OR gates also receives the signal A, B, Ci for AND gate-A4. The output of this gates is given to AND –gate-A5, which receives its second input for OR –gate-O1. Output of AND gate A5 output of AND-gate-O5 is sum output. So we obtain

$S_n = (A+B+C_i) (\overline{A.C\iota+B.C\iota+A.B+A.B.C\iota})$   $S_n = (A+B+C_i) (\overline{A.C\iota+B.C\iota+A.B+A.B.C\iota})$   $= (A+B+Ci) [(\overline{A}+\overline{C}\iota)(\overline{B}+\overline{C}\iota)(\overline{A}+\overline{B}) + (A.B.C_i)]$   $= (A+B+C_i) (\overline{A}.\overline{B} + \overline{A}.\overline{C} + \overline{A}.\overline{B}.\overline{C} + \overline{B}.\overline{C}\iota + A.B.C)$   $= A.\overline{B}.\overline{C}\iota + A.B.Ci + \overline{A}.B.\overline{C}i + \overline{A}.\overline{B}.C$

From the Fig-4 it is evident that electron from input to output is manipulated by intrinsic properties of hybrid CMOS-SET itself at different block interval with the incorporation of input signal.

As a consequence the propagation delay is controlled which minimizes the power dissipation of the proposed architecture, resulting high integration density of the model. Evidently, the robustness and the high performance increased its acceptability for IC configuration.

| Machine |      |                   |             |            |

|---------|------|-------------------|-------------|------------|

|         | Gate | Power Consumption | No. of CMOS | No. of SET |

|         | AND  | 0.01V             | 3           | 3          |

|         | OR   | 0.01V             | 3           | 3          |

|         | NOT  | 0.01V             | 1           | 1          |

Tables: Emperical study of power dissipation and power consumption of different device in the proposed phototype of IBM

Machine

### CONCLUSION

The authors here successfully presented a novel architecture of next generation advanced arithmetic circuit using Hybrid CMOS-SET. The perfect combination essentially delivers high speed output. Two main substantial heights have been achieved- 1) high speed low power consuming arithmetic circuit and 2) extremely fast computational speed. Hereby the authors conclude that such composition can be adhered for other sophisticated complex circuits.

### REFERENCES

- Y. Taur, "CMOS design near the limit of scaling", IBM J. RES. & DEV. VOL. 46 NO. 2/3 MARCH/MAY 2002.

- [2] H. Iwai, "CMOS downsizing toward sub-100 nm", Solid-State Electron., vol. 48, 2003, pp. 497-503

- [3] H. Iwai, "Future semiconductor manufacturing-challenges and opportunities", IEDM Tech. Dig., 2004, pp. 1-16

- [4] G. M. Whitesides and J. C. Love, 2001. "The Art of Building Small". Scientific American, September.

- [5] M. L. Roukes, 2001. "Plenty of Room, Indeed". Scientific American, September.

- [6] K. E. Drexler, 2001. "Machine-Phase Nanotechnology". Scientific American, September.

- [7] G.E. Moore: Electronics Magazine 1965 (Mc Graw Hill New york).

- [8] Pollack F. Intel 1999. In: The International Technology Roadmap for Semiconductors, 2005.

- [9] W. HAENSCH ET AL, "Silicon CMOS devices beyond scaling", IBM J. RES. & DEV. VOL. 50 NO. 4/5 JULY/SEPTEMBER 2006.

- [10] H. Iwai, "Roadmap for 22 nm and beyond", Microelectronic Engineering, 2009.

- [11] High-Performance / Low-Power 65nm CMOS Technology CS200 / CS200A, Fujitsu Microelectronics America, Inc. Conference Digest. International Quantum Electronics Conference (Cat. No.00TH8504) 2000

- [12] K.K. Berggren, "Quantum computing with superconductors," Proceedings of the IEEE, Oct. 2004, pgs. 1630 1638

- [13] Scott Aaronson, "The Limits of Quantum", 2008 SCIENTIFIC AMERICAN, INC.

- [14] Atsugi-shi, "Quantum information technology based on single electron dynamics", NIT basic research laboratories, 243-0198 Japan, Vol. 1 No.3 June 2003.

- [15] Amiza Rasmi & Uda Hashim "Single-electron transistor (SET): Literature Review" journal 2005, Koieg University, Malaysia.

- [16] P. Hadley, G. Lientschnig, and M. Lai, "Single-Electron Transistors," pp. 1-8.

- [17] Liu, R.S.; Pettersson, H.; Suyatin, D.; Michalak, L.; Canali, C.M.; Samuelson, L., "Nanoscaled ferromagnetic single-electron transistors", 7th IEEE Conference on Nanotechnology, 2007. IEEE-NANO 2007.

- [18] K. K. Likharev : IBM J. Res. Devel., vol 32, 144, 1988.

- [19] Santanu Mahapatra and Adrian Mihai Ionescu "Realization of multiple valued logic and memory by hybrid SETMOS architecture" IEEE transactions on Nanotechnology, Vol. 4, No. 6, November 2005.

- [20] S. Mahapatra, A.M. lonescu, K. Banejee, M.J.Declerq, "Modelling and analysis of power dissipation in single electron logic", Technical Digest of IEDM 2002.

http://www.ijesrt.com@International Journal of Engineering Sciences & Research Technology

[21] G.Lientsching, I.Weymann and P.Hadley "Simulating Hybrid Circuits of Single Electron Transistors and Field Effect Transistors" – Japanese Journal of Applied Physics, vol. 42, pp 6467 – 6472, 2003.

## **AUTHOR BIBLOGRAPHY**

|   | Dr. J Gope,<br>PhD (Engg.), & Chartered Engineer has received his PhD Degree<br>in Nanotechnology from Jadavpur University, Kolkata and is<br>presently associated with Camellia School of Engg and Tech,,<br>Barasat, West Bengal University of Technology<br>Kolkata, India, +91 9831205967 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | <b>Mr. Chowdhury Tousif Ahammed</b> , is a final year student of B.Tech in Electrical Engineering Department of Camellia School of Engineering and Technology, West Bengal, India.                                                                                                            |

| R | <b>Mr. Habibur Rahman,</b> is a final year student of B.Tech in Electrical Engineering Department of Camellia School of Engineering and Technology, West Bengal, India.                                                                                                                       |

## List of figure

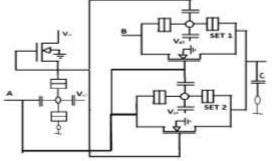

Fig1. Hybrid CMOS-SET based AND realization

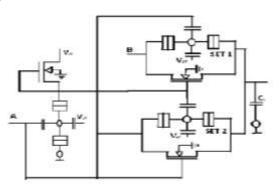

Fig 2. . Hybrid CMOS-SET based OR realization

Fig 3. Hybrid CMOS-SET based NOT realization

http://www.ijesrt.com@International Journal of Engineering Sciences & Research Technology

Fig 4. Hybrid CMOS-SET based IBM Machine Prototype